Verilog 复位简介

关键词: 同步复位, 异步复位

为确保系统上电后有一个明确、稳定的初始状态,或系统运行状态紊乱时可以恢复到正常的初始状态,数字系统设计中一定要有复位电路模块。复位电路异常可能会导致整个系统的功能异常,所以在一定程度上,复位电路的重要性也不亚于时钟电路。

复位电路可分类为同步复位和异步复位。

同步复位

同步复位是指复位信号在时钟有效边沿到来时有效。如果没有时钟,无论复位信号怎样变化,电路也不执行复位操作。

同步复位的典型代码描述如下:

module sync_reset(

input rstn, //同步复位信号

input clk, //时钟

input din, //输入数据

output reg dout //输出数据

);

always @(posedge clk) begin //复位信号不要加入到敏感列表中

if(!rstn) dout <= 1'b0 ; //rstn 信号与时钟 clk 同步

else dout <= din ;

end

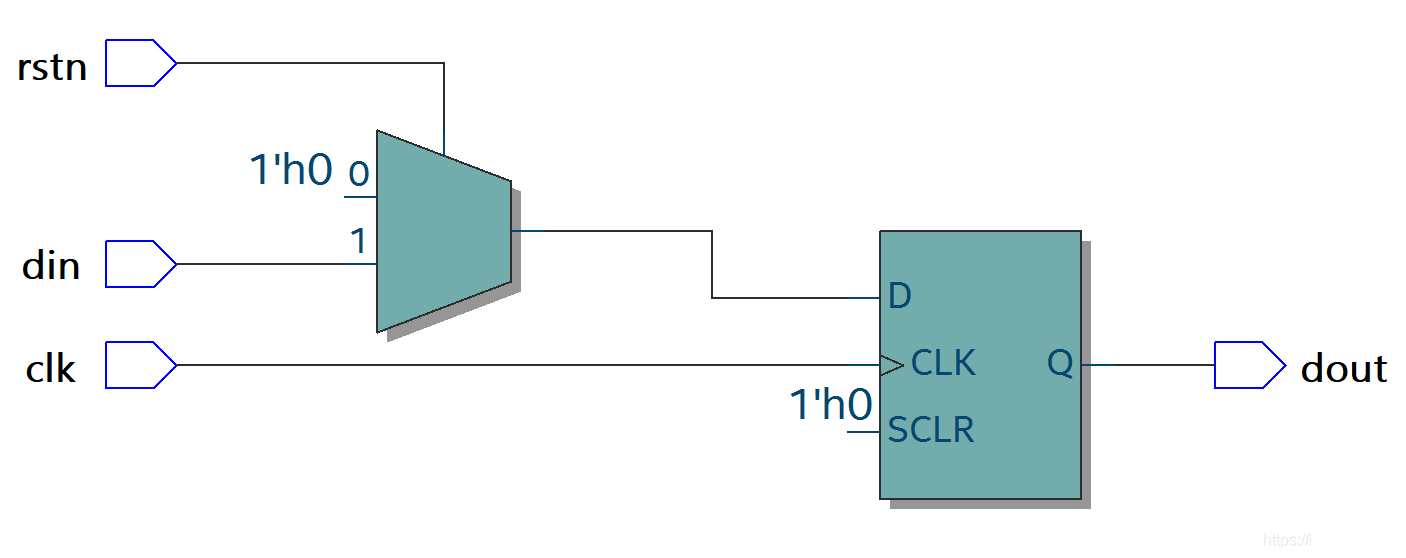

endmodule该描述代码常常会被综合成如下电路:

同步复位的优点:信号间是同步的,能滤除复位信号中的毛刺,有利于时序分析。

同步复位的缺点:大多数触发器单元是没有同步复位端的,采用同步复位会多消耗部分逻辑资源。且复位信号的宽度必须大于一个时钟周期,否则可能会漏掉复位信号。

异步复位

异步复位是指无论时钟到来与否,只要复位信号有效,电路就会执行复位操作。

异步复位的典型代码描述如下:

module async_reset(

input rstn, //异步复位信号

input clk, //时钟

input din, //输入数据

output reg dout //输出数据

);

//复位信号要加到敏感列表中

always @(posedge clk or negedge rstn) begin

if(!rstn) dout <= 1'b0 ; //rstn 信号与时钟 clk 异步

else dout <= din ;

end

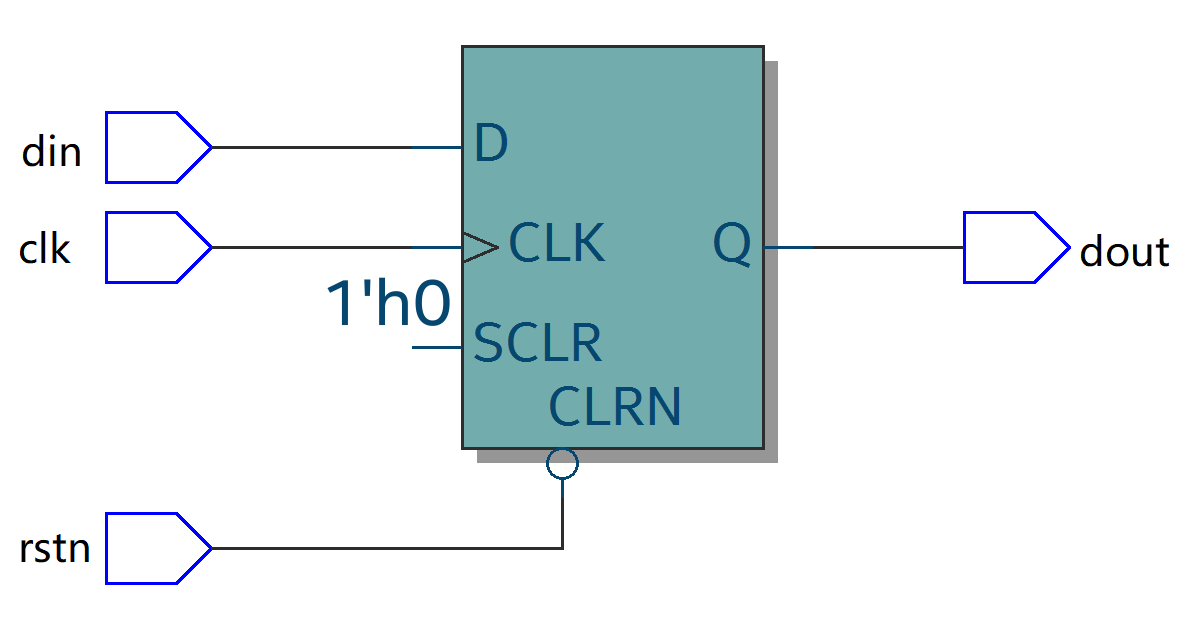

endmodule该代码常常会被综合成如下电路:

异步复位的优点:大多数触发器单元有异步复位端,不会占用额外的逻辑资源。且异步复位信号不经过处理直接引用,设计相对简单,信号识别快速方便。

异步复位的缺点:复位信号与时钟信号无确定的时序关系,异步复位很容易引起时序上 removal 和 recovery 的不满足。且异步复位容易受到毛刺的干扰,产生意外的复位操作。

异步复位同步释放

综合设计与资源等方面的考虑,一般数字系统设计时都会使用异步复位。

为消除异步复位的缺陷,复位电路往往会采用"异步复位、同步释放"的设计方法。即复位信号到来时不受时钟信号的同步,复位信号释放时需要进行时钟信号的同步。

异步复位、同步释放的典型代码描述如下:

module areset_srelease(

input rstn, //异步复位信号

input clk, //时钟

input din, //输入数据

output reg dout //输出数据

);

reg rstn_r1, rstn_r2;

always @ (posedge clk or negedge rstn) begin

if (!rstn) begin

rstn_r1 <= 1'b0; //异步复位

rstn_r2 <= 1'b0;

end

else begin

rstn_r1 <= 1'b1; //同步释放

rstn_r2 <= rstn_r1; //同步打拍,时序差可以多延迟几拍

end

end

//使用 rstn_r2 做同步复位,复位信号可以加到敏感列表中

always @ (posedge clk or negedge rstn_r2) begin

if (!rstn_r2) dout <= 1'b0; //同步复位

else dout <= din;

end

endmodule该代码描述常常会被综合成如下电路:

需要说明的是,复位电路会消耗更多的硬件逻辑和面积资源,增加系统设计的复杂性。不带复位端的触发器也具有相对较高的性能。所以在一些初始值不影响逻辑正确性的数字设计中,例如数据通路中一些数据处理的部分,高速流水线中的一些寄存器,可以考虑去掉复位以达到最佳性能。

为方便、快速的仿真非复位逻辑的其他功能,教程所有数字设计中的复位都是从 testbench 中引入异步复位,没有考虑复位电路的时序问题。实际设计数字系统时,一定要对复位电路进行单独、仔细、慎重的设计。

免费 AI IDE

免费 AI IDE

更多建议: